从系统架构入手,掌握高性能电机控制电路设计的三大核心策略

在电机及其控制系统的研发过程中,高性能控制电路的设计是实现精准、高效、可靠运行的关键。一个优秀的系统架构是这一切的基础。本文将从系统架构的顶层设计出发,为您揭示实现高性能控制电路的三大核心策略,助您在研发中事半功倍。

第一招:模块化与层次化架构设计

高性能控制电路的设计绝非简单的元件堆砌,首要策略是构建清晰、灵活的模块化与层次化系统架构。

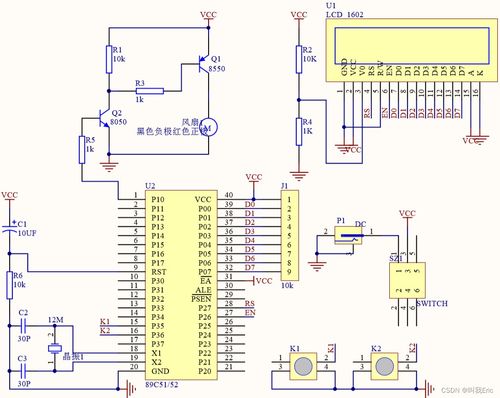

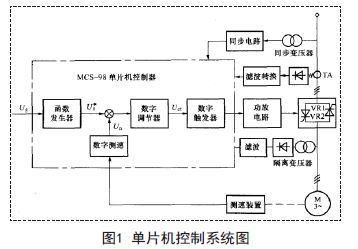

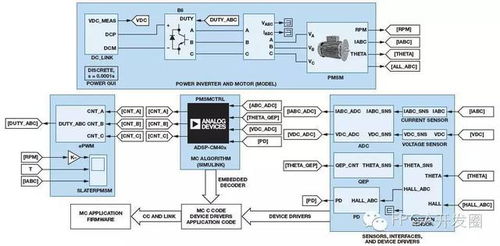

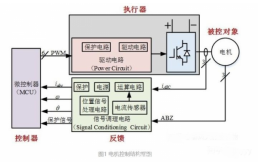

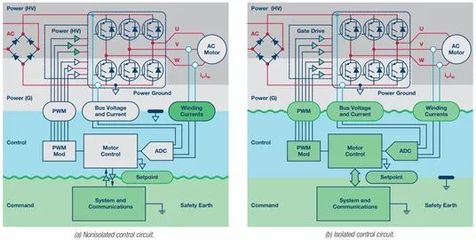

- 物理层分离:将功率驱动模块(如IPM模块、栅极驱动)、信号调理与采样模块(电流/电压/位置传感器接口)、核心计算模块(MCU/FPGA/DSP)以及通信接口模块(CAN、EtherCAT等)在物理布局和电气上进行明确分离。这能有效隔离大功率开关噪声对敏感信号电路的干扰,是提升系统信噪比与可靠性的根本。

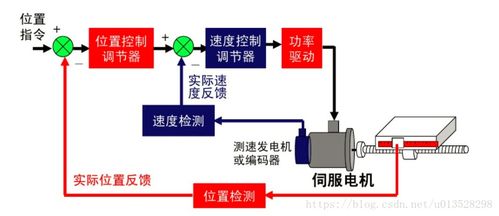

- 功能层抽象:在软件或硬件逻辑层面,建立分层的控制架构。通常包括:硬件抽象层(直接驱动外设)、控制算法层(执行FOC、SVPWM等核心算法)、应用管理层(处理通信、状态机、故障诊断)。这种抽象确保了算法的可移植性、可测试性,并便于团队协作与功能迭代。

- 数据流优化:在架构设计时,需精心规划关键数据(如相电流、转子位置、指令值)的采样、处理与反馈路径。采用并行处理、专用硬件加速器(如PWM生成单元、快速ADC)以及DMA传输,最大化减少控制延迟,提升系统带宽与动态响应速度。

第二招:精准的建模、仿真与参数辨识

脱离模型的高性能设计如同盲人摸象。第二招是在架构设计中深度融合建模与仿真,并实现关键参数的在线或离线辨识。

- 多领域协同仿真:在架构设计初期,就应建立包含电机电磁模型、功率电路开关模型、热模型以及控制算法模型的系统级仿真平台(如基于MATLAB/Simulink、PLECS)。通过仿真,可以预先评估架构合理性、算法性能极限,并对关键应力(电压、电流、温升)进行预测,从而指导硬件选型与电路参数设计,避免后期反复。

- 参数敏感度分析与辨识:电机参数(如定子电阻、电感、反电动势系数)会随温度、饱和度变化。在系统架构中,需预留参数辨识的接口与算力。通过设计专用的辨识算法(如注入高频信号、利用电机启停过程),在线或定期更新控制器参数,使系统始终运行在最优或接近最优的状态,这对于提升效率、降低转矩脉动至关重要。

- 数字孪生与硬件在环测试:将高保真度的电机与控制模型与真实的控制器硬件相结合,进行硬件在环测试。这允许在真实硬件上,于安全、低成本的环境下,对极端工况、故障场景进行反复测试,极大加速开发周期并验证架构的鲁棒性。

第三招:多维度的可靠性、安全性与电磁兼容设计

高性能必须建立在可靠与安全的基础之上。第三招是从系统架构的源头,注入可靠性、功能安全与电磁兼容性设计。

- 冗余与容错架构:对于高可靠性要求的应用(如航空航天、医疗、工业机器人),需在架构层面考虑冗余设计,如双路采样、双核锁步计算的MCU、冗余的电源与通信通道。设计具备容错能力的算法,当单一传感器失效时,能通过观测器等技术维持系统降级运行。

- 功能安全贯通设计:遵循ISO 26262(汽车)、IEC 61508(工业)等标准,从系统架构阶段就开始进行危害分析与风险评估。在硬件上,集成看门狗、电压监控、过流/过温/短路保护电路;在软件上,设计完善的状态监控、故障诊断与安全状态切换机制。确保故障能够被及时检测并安全处理。

- EMC的架构级管控:电磁兼容性问题必须从系统架构和PCB布局布线阶段进行压制。关键措施包括:

- 电源网络分层与去耦:为数字、模拟、功率地设计恰当的星点连接或分割方案,并在各电源节点就近布置高质量的去耦电容。

- 关键噪声路径抑制:优化功率回路(如直流母线)的布局以最小化寄生电感;为开关器件(MOSFET/IGBT)设计有效的吸收电路;对敏感信号线采用屏蔽、差分传输或远离噪声源。

- 滤波与接口防护:在所有电源入口和对外接口(通信、传感器)设置滤波与瞬态抑制器件,防止外部干扰侵入及内部干扰外泄。

高性能电机控制电路的设计,是一个从宏观架构到微观实现的系统性工程。模块化层次化的架构是骨架,确保了清晰与灵活;建模仿真与参数辨识是神经,赋予了系统精准的感知与优化能力;而可靠性、安全性与EMC设计则是免疫系统,保障了系统在复杂环境下的长期稳健运行。牢牢掌握这从系统架构入手的“三招”,并将其贯穿于研发的全生命周期,方能打造出真正卓越的高性能电机控制系统,在激烈的技术竞争中占据制高点。

如若转载,请注明出处:http://www.sfsh-skf.com/product/70.html

更新时间:2026-05-10 15:16:20